チェンナイでのPCB設計をお探しですか?

プリント回路基板、またはPCBは、機械的に支持し、非導電性基板上に積層銅板からエッチングされ、導電性経路、トラックまたは信号トレースを使用して、電子部品を接続するために使用されます。 また、プリント配線基板(PWB)またはエッチングされた配線基板と呼ばれています。 プリント回路基板は、実質的にすべてで使用されているが、最も簡単なものは、商業的に、電子デバイスを製造しました。

電子部品が実装されたPCBは、プリント回路アセンブリ(PCA)、プリント回路基板アセンブリ、またはPCBアセンブリ(PCBA)と呼ばれます。 非公式の使用では、「PCB」という用語は、裸のボードと組み立てられたボードの両方に使用され、文脈によって意味が明確になります。

PCBの回路特性

各トレースは、エッチング後に残る銅箔のフラット、狭い部分で構成されています。 トレースの幅と厚さによって決定される抵抗は、導体が運ぶ電流に対して十分に低くなければなりません。 電源とグランドのトレースが信号トレースよりも広くする必要があるかもしれません。 多層基板の一方の全体の層はシールドと電源復帰のための接地面として作用するほとんどの固体銅であってもよいです。

マイクロ波回路のために、伝送線は、一貫性のインピーダンスを保証するために慎重に制御された寸法を有するストリップライン及びマイクロストリップの形に配置することができます。 高周波および高速スイッチング回路、プリント回路基板導体のインダクタンスとキャパシタンスに有意な回路素子、通常は望ましくないとなります。 それらは追加のディスクリート部品を不要、回路設計の意図的な一部として使用することができます。

プリント回路アセンブリ

プリント回路基板(PCB)が完成したら、電子部品を取り付けて、機能的なプリント回路アセンブリまたはPCA(「プリント回路基板アセンブリ」PCBAと呼ばれることもあります)を形成する必要があります。 スルーホール構造では、コンポーネントのリード線が穴に挿入されます。 表面実装構造では、コンポーネントはPCBの外面のパッドまたはランドに配置されます。 どちらの種類の構造でも、コンポーネントのリード線は溶融金属はんだでボードに電気的および機械的に固定されています。

PCBの部品を取り付けるために使用されるはんだの種々の技術が存在します。 大量生産は通常のSMT配置機、バルク波のはんだ付けリフロー炉で行われますが、熟練した技術者は非常に小さな部品をはんだ付けすることができます(に0201をされているインスタンス0.02パッケージのために。0.01によってで。)手で顕微鏡下で、使用してピンセットと小容量のプロトタイプのための先端の細いはんだごて。 いくつかの部分は、BGAパッケージのように、手ではんだ付けすることは非常に困難であり得ます。

他の人が唯一のスルーホールパッケージで提供されていながら、いくつかの必要なコンポーネントは、唯一の表面実装パッケージで提供されていますので、多くの場合、貫通孔と表面実装構造は、単一のアセンブリに組み合わせなければなりません。 両方の方法を使用するもう1つの理由はそのまま行くことが期待されているコンポーネントは、表面実装技術を使用して、より少ないスペースを取るだろうしながら、スルーホール実装は、物理的なストレスに耐えると思わコンポーネントに必要な強度を提供することができることです。

ボードが取り込まれた後、それは、種々の方法で試験することができます。

電源がオフの間、目視検査、自動光学検査。 PCBの部品配置、はんだ付け、および検査用JEDECガイドラインは、一般的にPCB製造のこの段階での品質管理を維持するために使用されます。

電源がオフになっている一方で、アナログシグネチャ解析、電源オフテスト。

電力ではあるが上、インサーキットテスト、物理的測定(すなわち電圧、周波数)を行うことができる場所。

電源が機能テスト、上にある間、ちょうどPCBがそれを行うように設計されていたものないかどうかをチェックします。

これらのテストを容易にするために、PCBは、一時的な接続を行うために余分なパッドを設計することができます。 時には、これらのパッドは、抵抗器を用いて分離する必要があります。 インサーキットテストはまた、いくつかのコンポーネントのバウンダリスキャンテスト機能を行使することができます。 インサーキット試験システムはまた、基板上の不揮発性メモリ・コンポーネントをプログラムするために使用されてもよいです。

バウンダリスキャンテストでは、ボード上の各種のICに統合テスト回路はICが正しくマウントされていることをテストするために、PCBトレース間の一時的な接続を形成します。 バウンダリスキャンテストは、すべてのICは、標準的なテスト構成手順、JTAG(Joint Test Action Group)の標準が最も一般的なものの使用をテストすることが必要です。 JTAGテストアーキテクチャは、物理的なテスト・プローブを使用することなく、基板上の集積回路間の相互接続をテストするための手段を提供します。 JTAGツールベンダーは、失敗したネットを検出するために、だけでなく、特定のネット、デバイス、およびピンに障害を隔離するだけでなく、刺激と洗練されたアルゴリズムの様々な種類を提供します。

ボードがテストに失敗すると、技術者がDESOLDER、失敗したコンポーネント、リワークとして知られているタスクを置き換えてもよいです。

設計

プリント回路基板のアートワークの生成は、当初、完全に手動のプロセスで、通常は目的のサイズの2倍または4倍のスケールで透明なマイラーシート上で行われました。 回路図は最初にコンポーネントのピンパッドのレイアウトに変換され、次にトレースがルーティングされて必要な相互接続が提供されました。 事前に印刷された非複製マイラーグリッドがレイアウトを支援し、回路要素(パッド、コンタクトフィンガー、集積回路プロファイルなど)の一般的な配置の摩擦による乾式転写がレイアウトの標準化に役立ちました。 デバイス間のトレースは、粘着テープで作成されました。 完成したレイアウト「アートワーク」は、ブランクコーティングされた銅張板のレジスト層に写真で再現されました。

現代の実践は、コンピュータが自動的にレイアウト手順の多くを実行することができるので、少ない労働集約的です。 商業用プリント基板設計のための一般的な進行が含まれます:

電子設計自動化ツールを使用して回路図キャプチャ。

カードの寸法とテンプレートが必要な場合は、固定部品とヒートシンクを決定するのに必要な回路やケースに基づいて決定されます。

PCBのスタック層を決定します。 1は、設計の複雑さに応じて複数の層を12たりします。 グランドプレーンと電源プレーンが決定されます。 信号が配線されている信号プレーンは、トップ層だけでなく、内部層です。

誘電体層の厚さ、配線の銅厚さおよびトレース幅を使用して、ラインインピーダンス決意。 トレース分離はまた、差動信号の場合に考慮します。 マイクロストリップ、ストリップラインまたは二重ストリップラインは、ルート信号に使用することができます。

コンポーネントの配置。 熱に関する検討事項と形状が考慮されます。 ビアとランドがマークされています。

信号トレースをルーティング。 電源プレーンは、AC用のグランドとして振る舞うように、最適なEMIの性能のために高周波信号が電源またはグランドプレーン間の内部層に配線されています。

製造用ガーバーファイルの生成。

多層プリント配線板

地面に層を捧げるためのオプション

信号用の基準面を形成します

EMIコントロール

単純なインピーダンス制御

電源電圧にレイヤーを捧げるためのオプション

低ESL / ESR配電

信号のためのより多くの配線リソース

素材の選択の電気に関する注意事項

誘電率(誘電率)

より良い、より安定しました

低い値が高い層数のために、より適切であり得ます

より高い値は、いくつかのRF構造のために、より適切であり得ます

損失正接

低い、より良いです

高い周波数で問題のよりになります

吸湿

低い、より良いです

誘電定数と損失正接を行うことができます

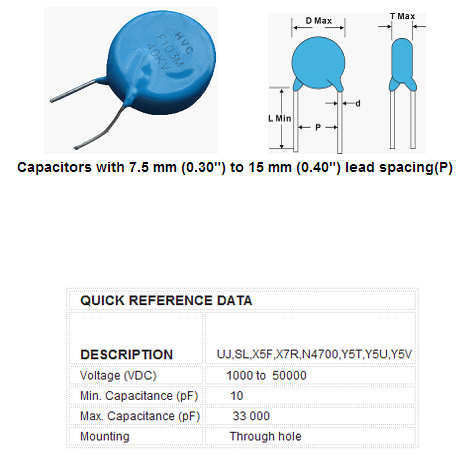

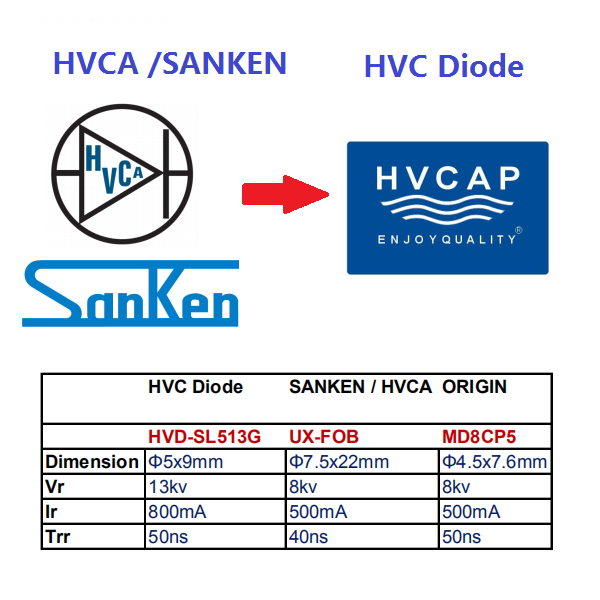

電圧破壊

より良い、より高いです

高電圧用途を除いて一般的に問題ではありません、

抵抗率

より良い、より高いです

低リーク用途を除いて一般的に問題ではありません、